-

이재용, 벨기에 아이멕과 논의한 신무기… “웨이퍼 앞뒷면 다 쓴다”지금 이곳에선 2022. 10. 28. 00:15

이재용, 벨기에 아이멕과 논의한 신무기… “웨이퍼 앞뒷면 다 쓴다”

반도체, 미세공정 위한 여러 방안 개발

3나노부터 세계 최초 GAA 적용한 삼성

3차원 개념 도입하는 초미세공정

이재용 부회장, 6월 기술 제안한 벨기에 imec 방문

삼성전자가 세계 최초로 양산에 성공한 3나노 파운드리 반도체. 삼성전자는 여기에 GAA라는 새 구조를 도입했다. /삼성전자 제공

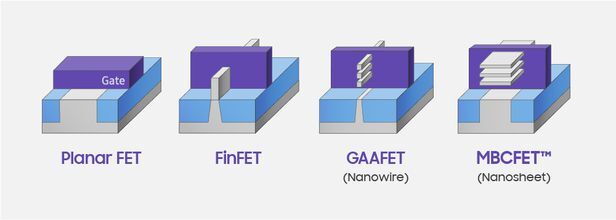

입력 2022.10.27 06:00삼성전자 파운드리(반도체 위탁생산)가 2025년 2㎚(나노미터·10억분의 1m), 2027년 1.4㎚ 공정에 웨이퍼(반도체 원판)의 뒤쪽 면을 활용하는 기술을 도입한다. 기존 2차원(2D)적인 반도체를 3차원(3D)으로 확장하는 것이다. 해당 기술은 유럽 최대 종합반도체 연구소 imec(아이멕)이 최초 고안한 것으로, 이재용 부회장이 지난 6월 imec을 찾아 이와 관련한 논의를 나눈 것으로 알려졌다. 삼성전자는 3㎚ 공정에서 게이트올어라운드(GAA)라는 새구조를 처음으로 상용화한 만큼 2㎚ 공정에서도 1위 TSMC에 기술 우위를 점하겠다는 전략을 세웠다. 반도체 트랜지스터 구조도. 왼쪽에서 두번째가 5나노 시대까지 주를 이뤘던 핀펫(FinFET) 구조다. 삼성전자는 GAA(왼쪽에서 세번째)로 불리는 새 구조를 개선한 독자 기술 MBCFET을 고안, 3나노 공정에 활용하고 있다. /삼성전자 제공27일 반도체 업계에 따르면 삼성전자는 2㎚ 공정부터 웨이퍼의 뒤쪽을 활용하는 기술 ‘BSPDN(백사이드파워딜리버리네트워크)’을 활용한다. 이 기술은 반도체 성능 한계를 뛰어넘기 위해 고안된 것으로, 지난 2019년 벨기에 루벤에 있는 유럽 최대 종합반도체 연구소 imec이 제안한 개념이다.최근 삼성전자 파운드리의 기술개발 연구직원이 국내 반도체 포럼에서 이런 내용을 발표해 화제가 됐다.전기 신호에 의해 작용하는 반도체는 전류를 어떻게 흘려보내는 지가 기술의 핵심이다. 반도체 성능과 효율을 동시에 높이는 공정 미세화가 진행될수록 전류 흐름은 더욱 중요해졌고, 이전 기술로는 한계가 명확했다.이를 해결한 것이 인텔이 2011년 처음 상용화한 핀펫(FinFET) 구조다. 전류가 지나는 통로를 3개 만들어 마치 지느러미(핀)처럼 ‘凸(볼록할 철)’ 모양으로 배치한 것이다.핀펫 구조도 더 세밀한 회로에서는 이전과 같은 문제가 발생했다.해결을 위해 전류가 흐르는 통로 상하좌우 4면을 ‘回(돌아올 회)’처럼 감싸는 GAA 기술이 나타났다. GAA는 구조 특성상 전류 흐름성이 더 좋아질 수밖에 없는 구조여서 세밀한 회로를 그리는 게 가능했지만 상용화한 회사는 없었다.삼성전자는 GAA를 개선한 MBCFET 구조를 독자 개발해 3㎚ 공정에 최초 적용, 초미세공정을 선도하기 시작했다. TSMC는 3㎚ 공정까지 기존의 핀펫을 유지하고, 그 이하 공정부터 GAA를 도입한다는 계획이지만, 삼성전자가 3㎚ 양산을 시작한지 4개월이 지나도록 양산 소식이 들려오고 있지 않다. 오히려 내년으로 양산이 연기될 가능성이 점쳐진다.

반도체 트랜지스터 구조도. 왼쪽에서 두번째가 5나노 시대까지 주를 이뤘던 핀펫(FinFET) 구조다. 삼성전자는 GAA(왼쪽에서 세번째)로 불리는 새 구조를 개선한 독자 기술 MBCFET을 고안, 3나노 공정에 활용하고 있다. /삼성전자 제공27일 반도체 업계에 따르면 삼성전자는 2㎚ 공정부터 웨이퍼의 뒤쪽을 활용하는 기술 ‘BSPDN(백사이드파워딜리버리네트워크)’을 활용한다. 이 기술은 반도체 성능 한계를 뛰어넘기 위해 고안된 것으로, 지난 2019년 벨기에 루벤에 있는 유럽 최대 종합반도체 연구소 imec이 제안한 개념이다.최근 삼성전자 파운드리의 기술개발 연구직원이 국내 반도체 포럼에서 이런 내용을 발표해 화제가 됐다.전기 신호에 의해 작용하는 반도체는 전류를 어떻게 흘려보내는 지가 기술의 핵심이다. 반도체 성능과 효율을 동시에 높이는 공정 미세화가 진행될수록 전류 흐름은 더욱 중요해졌고, 이전 기술로는 한계가 명확했다.이를 해결한 것이 인텔이 2011년 처음 상용화한 핀펫(FinFET) 구조다. 전류가 지나는 통로를 3개 만들어 마치 지느러미(핀)처럼 ‘凸(볼록할 철)’ 모양으로 배치한 것이다.핀펫 구조도 더 세밀한 회로에서는 이전과 같은 문제가 발생했다.해결을 위해 전류가 흐르는 통로 상하좌우 4면을 ‘回(돌아올 회)’처럼 감싸는 GAA 기술이 나타났다. GAA는 구조 특성상 전류 흐름성이 더 좋아질 수밖에 없는 구조여서 세밀한 회로를 그리는 게 가능했지만 상용화한 회사는 없었다.삼성전자는 GAA를 개선한 MBCFET 구조를 독자 개발해 3㎚ 공정에 최초 적용, 초미세공정을 선도하기 시작했다. TSMC는 3㎚ 공정까지 기존의 핀펫을 유지하고, 그 이하 공정부터 GAA를 도입한다는 계획이지만, 삼성전자가 3㎚ 양산을 시작한지 4개월이 지나도록 양산 소식이 들려오고 있지 않다. 오히려 내년으로 양산이 연기될 가능성이 점쳐진다. 그래픽=이은현BSPDN은 이보다 한 차원 수준이 높은 기술로 여겨진다. 전류 흐름을 원활하게 하기 위해 구조를 바꾸는 게 아니라 웨이퍼 뒤쪽에 전기 전달을 위한 구조를 짜는 것이다. 현재 반도체가 웨이퍼 한쪽만을 사용하는 2D 형태라면, BSPDN은 웨이퍼의 앞뒤를 모두 사용하는 3D 형태다.웨이퍼 전면에는 논리적인 연산 작업을 수행하는 로직 기능으로만 채우고, 후면에는 전력이나 신호 전달(라우팅) 기능을 넣는다. 그렇게 되면 기존에 로직과 전력, 신호 라우팅이 모두 빡빡하게 들어가던 웨이퍼 전면에 여유가 생기고, 보다 세밀한 회로를 새길 수 있게 된다는 원리다.

그래픽=이은현BSPDN은 이보다 한 차원 수준이 높은 기술로 여겨진다. 전류 흐름을 원활하게 하기 위해 구조를 바꾸는 게 아니라 웨이퍼 뒤쪽에 전기 전달을 위한 구조를 짜는 것이다. 현재 반도체가 웨이퍼 한쪽만을 사용하는 2D 형태라면, BSPDN은 웨이퍼의 앞뒤를 모두 사용하는 3D 형태다.웨이퍼 전면에는 논리적인 연산 작업을 수행하는 로직 기능으로만 채우고, 후면에는 전력이나 신호 전달(라우팅) 기능을 넣는다. 그렇게 되면 기존에 로직과 전력, 신호 라우팅이 모두 빡빡하게 들어가던 웨이퍼 전면에 여유가 생기고, 보다 세밀한 회로를 새길 수 있게 된다는 원리다. 이재용 삼성전자 부회장이 벨기에 루벤에 위치한 유럽 최대 종합 반도체 연구소 imec을 찾아 루크 반 덴 호브 CEO와 미래 기술에 대해 논의하고 있다. /삼성전자 제공imec이 지난해 세계 최고 권위의 반도체 학회인 ‘VLSI 심포지엄’에서 발표한 논문에 따르면 BSPDN 기술을 활용할 경우 기존 웨이퍼 전면만으로 만들어진 반도체에 비해 성능과 효율이 월등히 높아진다. 구조 단순화에 따른 효과인 것이다.여기에 더 세밀한 회로가 그려지면 초미세공정으로 인한 시너지 효과도 기대할 수 있다.업계 관계자는 “삼성전자가 3㎚로 앞선 초미세공정 경쟁에서 한 발짝 멀리 나가기 위해 승부수를 띄운 것으로 해석된다”라며 “기술을 주도하는 회사라는 신호를 시장에 던져줄 수 있을 것으로 기대된다”고 했다. 한편, 이 BSPDN 기술을 완성하기 위해서는 반도체 전체 공정 혁신도 필요하다. 지금까지와는 전혀 다른 개념의 기술이기 때문에 기존보다 훨씬 더 정교한 공정 기술이 도입돼야 하는 것이다.특히 물리적 연결을 위한 접합 기술이 상당히 중요하다.앞서 지난 6월 이재용 삼성전자 부회장은 BSPDN이라는 개념을 처음 제안한 imec의 벨기에 루벤 본사를 찾아 루크 반 덴 호브 최고경영자(CEO)와 만났다. 이 자리에서 두 CEO는 반도체 분야 최신 기술과 연구개발 방향 등을 논의했는데, 업계는 당연히 이 자리에서 2㎚ 공정에 대한 얘기가 오갔을 것으로 보고 있다.

이재용 삼성전자 부회장이 벨기에 루벤에 위치한 유럽 최대 종합 반도체 연구소 imec을 찾아 루크 반 덴 호브 CEO와 미래 기술에 대해 논의하고 있다. /삼성전자 제공imec이 지난해 세계 최고 권위의 반도체 학회인 ‘VLSI 심포지엄’에서 발표한 논문에 따르면 BSPDN 기술을 활용할 경우 기존 웨이퍼 전면만으로 만들어진 반도체에 비해 성능과 효율이 월등히 높아진다. 구조 단순화에 따른 효과인 것이다.여기에 더 세밀한 회로가 그려지면 초미세공정으로 인한 시너지 효과도 기대할 수 있다.업계 관계자는 “삼성전자가 3㎚로 앞선 초미세공정 경쟁에서 한 발짝 멀리 나가기 위해 승부수를 띄운 것으로 해석된다”라며 “기술을 주도하는 회사라는 신호를 시장에 던져줄 수 있을 것으로 기대된다”고 했다. 한편, 이 BSPDN 기술을 완성하기 위해서는 반도체 전체 공정 혁신도 필요하다. 지금까지와는 전혀 다른 개념의 기술이기 때문에 기존보다 훨씬 더 정교한 공정 기술이 도입돼야 하는 것이다.특히 물리적 연결을 위한 접합 기술이 상당히 중요하다.앞서 지난 6월 이재용 삼성전자 부회장은 BSPDN이라는 개념을 처음 제안한 imec의 벨기에 루벤 본사를 찾아 루크 반 덴 호브 최고경영자(CEO)와 만났다. 이 자리에서 두 CEO는 반도체 분야 최신 기술과 연구개발 방향 등을 논의했는데, 업계는 당연히 이 자리에서 2㎚ 공정에 대한 얘기가 오갔을 것으로 보고 있다.'지금 이곳에선' 카테고리의 다른 글

20억 넘던 잠실 집주인 멘붕"…강남도 '팔자' 매물 넘친다 (0) 2022.10.28 빅테크 시총 1년 만에 4000조 증발… 메타는 시총 20위권 밖으로 (0) 2022.10.28 정부, 카카오 무료서비스 보상 가이드라인 검토 (0) 2022.10.28 내년 고용허가제 외국인력 역대 최대 11만명 “조선업 최우선 배분” (0) 2022.10.28 “강남아파트 너마저”… 안전자산 일제히 추락에 자산가들 ‘고민’ (0) 2022.10.26